The conventional way of performing NAND Flash memory system level analysis primarily includes the effect of intersymbol interference (ISI), crosstalk (XTALK) and simultaneous switching noise (SSN) [1]. There are very few studies found in the industry focusing on the duty cycle distortion (DCD) jitter impact the NAND Flash memory system, especially at higher performance and higher load count. This paper focuses on the importance of DCD jitter analysis at higher speed and heavier loading NAND systems, and introduces a statistical approach to DCD jitter analysis.

Figure 1 provides a typical NAND Flash system representation for Read operations. During a Read operation, the Flash management controller (FMC) activates RE/BRE signals and sends them to the NAND RE/BRE I/O pads. RE/BRE signals then travel through the NAND Flash internal logic path and enable DQS/BDQS and data (DQ [7:0]) transfer to the FMC.

RE signal DCD is contributed by the following two components:

• FMC RE DCD: ONFI spec allows 5% DCD by the FMC.

• NAND Flash internal RE DCD: RE clock at NAND input is distorted by NAND internal logic circuitry passing out of NAND as DQS launches back to the FMC.

The total RE signal DCD can be approximately 10%~13% in a system, depending on data rates.

Figure 1: Block diagram of NAND Flash System

Conventional NAND Flash system analysis performs the simulation with 50% duty cycle random data pattern, the duty cycle distortion (DCD) impact is subtracted from the valid timing budget directly as shown in Equation 1 [2,3].

Actual_tDVW = UI – REDCD – SimulatedtQHS – SimulatedtDQSQ – SpectQHS – SpectDQSQ (1)

However, when we apply this analysis method on an 8-die @ 400Mbps NAND system, the simulation results showed many fewer degradations as compared to the real measured data. (as shown in Figure 2)

Figure 2: DQ and DQS Simulation vs. Measurement Data

The major limitation of the conventional DCD analysis method is that it ignores jitter amplification. It has been validated by previous studies that jitter (including SJ, DCD and RJ) can be amplified by a lossy channel even when the channel is linear, passive, and noiseless. And the effect grows exponentially with insertion loss and data rate [4,5,6,7] (as shown in Figure 3). It is worth pointing out that input jitter also causes amplitude modulation in the output signal, resulting in eye height impairment.

Figure 3: DCD amplification factors as functions of Date Rate & Insertion Loss

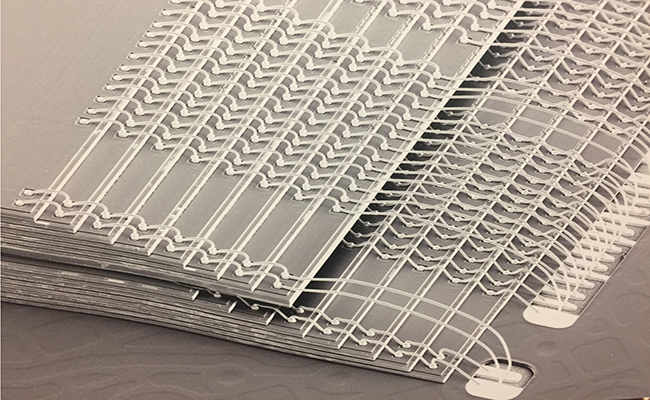

Due to the aggressive storage capacity requirements, multiple NAND Flash memory die are stacked in a highly integrated complex package system. Because of the cost-effective package solution used, imperfect ground reference, and wirebond connections, the return loss and insertion loss get progressively worse for higher speed and heavier loading Flash systems (as shown in Figure 4 and Figure 5).

The DCD jitter amplification and the jitter-induced amplitude modulation becomes more critical for new generation NAND Flash systems.

Figure 4: Simple 3D view of a highly integrated NAND Flash memory package

Figure 5: Return loss and Insertion loss of 2-die, 4-die and 8-die package

Limitation of SPICE-Like Simulator

To resolve the limitation in conventional methods, we performed transient simulation on an 8-die embedded system at 400MBPs with a non-ideal duty cycle input signal in HSPICE (Figure 6). As expected, by introducing the real duty cycle signal in system simulation, the jitter amplification and the DCD induced amplitude modulation are both well accounted for in the simulation.

Figure 6: Effect of duty cycle distortion (DCD) jitter on DQ (left) and DQS (right) signals

However, most SPICE-like simulators do not provide a non-ideal duty cycle input signal source, so a special Verilog-A based source module had to be developed. Also, the high simulation cost becomes another major barrier to using a SPICE-like simulator for systematic DCD analysis. (For example, for a typical 1-byte NAND system, HSPICE took around 5 hours to generate a several-hundred bits waveform.) The next section introduces a statistical-based simulation approach (ADS DDR BUS Simulator) to analyze the DCD impact systematically and more efficiently.

DCD Jitter Analysis with Statistical Simulation Approach

The statistical simulation methodology was developed and widely used for high-speed SERDES and memory systems such as PCIe4 or DDR4 [9]-[10]. It calculates eye distribution probability directly at ultra-low BER, without running an actual bit sequence at any desired BER level (as shown in Figure 7). This approach offers an extremely fast means of measuring the eye opening at ultra-low BER levels.

Figure 7: Statistical Simulation Approach

Figure 8 shows the transient (SPICE like) simulation and statistical simulation correlation results on a 2-Die Flash NAND test case at 800MBPs, the statistical method provides excellent correlation to the transient simulation, but in a much faster simulation time.

Figure 8: Comparison of Transient and Statistical Simulations

A 1-byte NAND simulation test bench was created in ADS as shown in Figure 9. An ADS batch-mode simulation controller was used with the DDR BUS simulator to sweep all variables and channel models automatically as described in Table 1.

|

Simulation Parameters |

Sweep Values |

|

Data Rate |

400M, 600M, 800M, 1066M and 1200M Bps |

|

Channel Models |

2-Die, 4-Die, 8-Die S parameter models |

|

DCD (UI) |

0.03, 0.06, 0.09, 0.12 |

|

IBIS Models |

BICS4_256G_EX3_VLV_2P I/O Buffers IBIS model |

Table 1 Simulation Space

Figure 9: 1-Bite NAND System Simulation Test Bench

The simulation finished in 6 mins for all 15 sweep cases. Figure 10 shows the eye-diagrams of DQ5 at 1200MBps. Significant eye shrinkage was observed when the DCD and die numbers increased. For the 0.12 UI DCD, 8-die design case, the simulated eye-diagram already violated the eye mask specification.

Figure 10: Statistical Eye-Diagram results at different Die number and DCD values

In addition to the eye-diagrams, the eye-height (EH) and eye-width (EW) were also measured at the 1E-12 BER level. The EH and EW shrinkages, normalized by the original EH and EW of the non-DCD case, were calculated based on the simulation results.

Figure 11 shows the DCD induced EW shrinkage increase linearly with the DCD. However, the DCD amplification was observed in all the simulation cases. The worst case was seen at the 1200Mbps and 8-die case, the 12% DCD input jitter caused about 37% EW shrinkage.

Figure 11: DCD induced EW shrinkage as a function of DCD

Also, Figure 12 shows that the DCD-induced EW shrinkage increases exponentially with the data-rate and die number. This is because more stacked dies will induce more insertion loss and return loss in the channel. This is consistent with the jitter amplification factor increasing trend as shown in Figure 3.

Figure 12: DCD induced EW shrinkage as a function of Data Rate and Die Number

Finally, a significant amplitude degradation was observed in a real measurement. This is because any input jitter will induce amplitude modulation in the output signal due to channel dispersion, leading to voltage noise at the channel output. The EH shrinkage was also predicted by the simulation as shown in Figure 13. The normalized EH shrinkage also increased exponentially with the data-rate.

Figure 13: DCD induced EH shrinkage as a function of Data Rate

Conclusions

The impact of RE duty cycle distortion (DCD) must be integrated in NAND FMC. And SI simulation should be done to predict system level performance accurately in a multi-die, high performance system. The conventional DCD analysis approach assumes the DCD-induced EH and EW will be linear at all the data rates so it will under-estimate the DCD impact, especially at higher data-rate and heavier-loading NAND system.

This paper proposes a new, statistical-based, system level NAND SI simulation methodology for more accurate DCD-included jitter and noise analysis. Comparing to the traditional SPICE-like simulator, this statistical-based approach provides a much faster simulation speed and an easier way to insert the RE DCD jitter into the input signal.

This paper has been modified from its original form, which was presented at DesignCon 2018 and won a Best Paper Award at the event.

Author(s) Biography:

Sayed Mobin is a senior manager with the Western Digital NAND Flash Memory Organization. He received his Master’s degree in electrical engineering from Virginia Tech, VA and his Bachelor’s degree in electrical engineering from Bangladesh University of Engineering Technology, Bangladesh. He has led the Western Digital NAND Flash SI team for the last four years. His focus is to evolve the signal integrity and power delivery infrastructure in Western Digital’s SanDisk Memory organization; provide critical decisions in future I/O design; and support both internal business units and external customers. Before Western Digital, he worked as a signal integrity lead at NVidia, focusing on mobile handheld system development for six years; as a signal integrity engineer at Intel Corporation for six years, focusing on signal integrity and power delivery solutions for wafer and package-level test environments; and conducted research in innovative solutions for multicore testing.

Cindy Cui is an application engineer with the EEsof Team at Keysight Technologies, Inc. She received her Master’s degree in micro-electronics from Tianjin University. She has over six years of service and support experience on high-speed digital, RFIC design, and device modeling at Keysight. Her focus is mainly on DDR4 Design, PCIe, IBIS modeling, and the correlation between simulation and measurement. Cindy has authored several technical papers in the field of high-speed design.

References:

[1] R. Micheloni, L. Crippa and A. Marelli, “Inside NAND Flash Memories”

[2] “ONFI specification version 2.0”, Feb 27, 2008

[3] “ONFI specification version 4.0”, Apr 2, 2014

[4] S. Chaudhuri, W. Anderson, J. McCall, and S. Dabrai, “Jitter amplification characterization of passive clock channels at 6.4 and 9.6 Gb/s,” Proc. IEEE 15th Topical Meeting on Electric Performance of Electronic Packaging, Scottsdale, AZ, Oct. 2006, pp. 21-24.

[5] C. Madden, S. Chang, D. Oh and C. Yuan, “Jitter Amplification Considerations for PCB Clock Channel Design,” IEEE 16th Topical Meeting on Electric Performance of Electronic Packaging, Atlanta, GA, pp. 135-138, Oct. 2007.

[6] F. Rao, V. Borich, H. Abebe and M. Yan, “Rigorous modeling of transmit jitter for accurate and efficient statistical eye simulation,” IEC DesignCon, Feb. 2010

[7] F. Rao and S. Hindi, “Frequency domain analysis of jitter amplification in clock channels,” Proc. IEEE 21st Topical Meeting on Electric Performance of Electronic Packaging, Tempe, AZ, Oct. 2012, pp. 51-54. https://literature.cdn.keysight.com/litweb/pdf/5991-1255EN.pdf?id=2239889

[8] S. Mobin, B. Raghunathan, A. Katz, “Impact of Read Enable (RE) Signal Duty Cycle Distortion (DCD) in NAND Flash SI Simulation”, EPEPS, Oct. 2017

[9] H. Lee, C. Cui, H. Barnes and L. Boluna “Accurate Statistical-Based DDR4 Margin Estimation using SSN Induced Jitter Model” DesignCon, Jan. 2017

[10] Y. Li, C. Morrison, F. Rao, C. Cui and G. Zhang “End-to-End System-Level Simulations with Repeaters for PCIe Gen4: A How-To Guide” DesignCon, Jan. 2017