If you are a big fan of Chiphead, you know that the end of January means it is time to gather in the Santa Clara Convention Center for DesignCon. This conference and exhibition provides an opportunity for the latest work in high-speed digital design to get a full airing, with some of the greatest minds in one place to ask the tough questions and bring new ideas together.

Here are some of the products and papers that you can see at DesignCon 2017.

Simberian: Booth 527

Simbeor THz electromagnetic signal integrity software will be demonstrated live at Simberian’s booth #527. Simbeor THz provides a systematic approach to interconnect design that starts from the material model identification and guarantees the analysis to the measurement correlation at the end. The latest version of Simbeor THz features multi-level parallelization in local network or in cloud, as well as an improved 3DTF field solver, PAM-4, and new dielectric models. The following live demos will be scheduled for every hour or provided on demand:

- S-parameters quality assurance and improvement;

- Broadband dielectric and conductor roughness models identification with GMS-parameters, SPP and new Gamma-T techniques;

- Pre-layout electromagnetic analysis and optimization of interconnects to minimize reflections and cross-talk;

- Post-layout electromagnetic analysis and validation of interconnects with signals up to 56 Gbps or bandwidth up to 50 GHz;

- Unique 3D visualization of EM fields and power flow density in typical interconnect structure with explanation of “How Interconnects Work”.

Simberian’s founder, Dr. Y. Shlepnev will be also co-presenting the following papers:

“Cost-effective PCB Material Characterization for High-volume Production Monitoring”, February 1st, 8:00-8:45am and “Back to basics: The onset of skin-effect in circuit board traces”, February 1st, 10:00-10:45am. More information: www.simberian.com

Samtec: Booth 717

On Thursday, February 2, Samtec’s Director of Signal Integrity Jim Nadolny will be presenting a 45-minute technical paper session covering “Design of Flyover QSFP28 (FQSFP Series) for 56+ Gbps Applications.” This presentation will demonstrate how Samtec achieved at least four times lower trace insertion loss with FQSFP for 56+ Gbps applications by replacing typical PCB trace based QSFP with flyover twinax cables to connect the receiver circuit to the port.

This product demonstration will showcase a disaggregated computing platform with PCIe® Gen 3 fabric enabled by the patented FireFly™ mid-board technology. By using PCIe-over-fiber, storage and GPU can be located 100 meters away, demonstrating a potential way to enable new HPC/data center architectures.

In the booth, Samtec will be showcasing:

Samtec’s flyover QSFP28 cable assembly (FQSFP Series), which boasts 28 Gbps performance and is backward compatible with QSFP assemblies. This direct-attach system, with press-fit tails that provide low speed signals and power to the PCB, allows drivers to be remotely located.

- ExaMAX® is a high-speed backplane system (EBTM/EBTF-RA Series) for 28 Gbps performance on a 2.00 mm column pitch with a roadmap to 56 Gbps. This system claims the industry’s lowest mating force, a 2.4 mm contact wipe and two points of contact. It exceeds OIF CEI-28G-LR for 28 Gbps standards and meets the Telcordia GR-1217 CORE specification.

- Edge Rate® HD: Samtec’s new 0.635 mm pitch, high-speed, multi-row strip - packages feature the same contact system found in the SEARAY™ family in a smaller and higher-density strip design. The four-row (5 mm wide) and two-row (2.5 mm wide; in development) versions can support 28+ Gbps applications, as well as multiple next-generation protocols

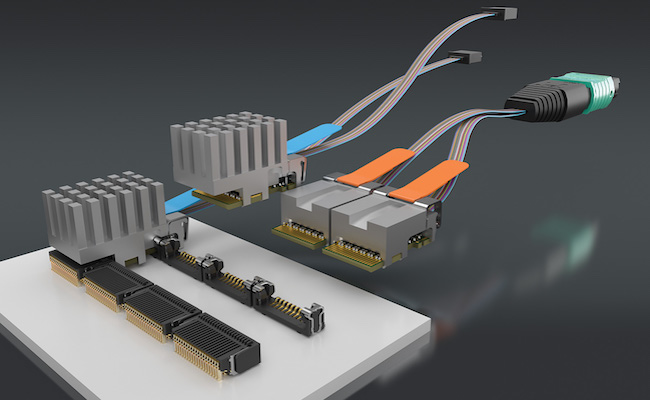

- FireFly: Samtec’s x4 duplex 28 Gbps FireFly™ optical engine (ECUO Series) targets the 100 Gbps datacom/telecom and HPC markets. Designed with thermal optimization in mind, options are available for forced air and cold plate cooling scenarios. The integral dual-band CDR was designed to work with the latest Ethernet and InfiniBand™ protocol specifications. Featuring a x4 duplex architecture and small footprint on the board, this product line targets communications within a rack, or between racks.

Figure 1: Samtec’s x4 duplex 28 Gbps FireFly optical engine

Mentor Graphics: Booth 1043

See Mentor Graphics Announces DesignCon Highlights (previously covered elsewhere on the Signal Integrity Journal).

Rohde & Schwarz: Booth 841

Rohde & Schwarz is showcasing its test and measurement solutions at DesignCon 2017 expo from February 1 to 2 in Santa Clara, CA, at booth #841. The company is featuring its test solutions for challenges in high-speed digital design and signal integrity as well as its latest power integrity measurement solutions. The setups cover crosstalk measurements, PAM-4 measurements, high bit rate channel characterization, low noise probing for signal integrity, battery life analysis and high speed PCB probing and power integrity. Products showcased include high-end vector network analyzers such as the R&S ZNB up to 40 GHz and the R&S ZNBT multiport VNA up to 20 GHz, but also oscilloscopes such as the R&S RTO2000 and the corresponding probes portfolio.

Figure 2: Rohde & Schwarz ZNBT multiport VNA

Rohde & Schwarz specialists will share their expertise in sponsored seminar sessions including:

- Characterization of Signal Integrity Using S-parameters

- Measuring Jitter Using Phase Noise Techniques

- Power Integrity Measurements: Challenges and Best Practices

- Understanding Probes and Probing Techniques for Signal and Power Integrity

- Frequency Domain Methods for Measuring Signal and Power Integrity

- An Introduction to Crosstalk Measurements

Cadence: Booth 515

In booth #515, Cadence will be demonstrating how you can optimize your signal and power integrity design and analysis and get support for PCIe® 4.0 support. A full summary of Cadence highlights at DesignCon, including technical sessions, panelists, and sponsored sessions are listed here.

Cadence booth demos will highlight:

- Constraint-driven power integrity design and analysis featuring easy setup with automated model and source/sink assignments

- Power-aware simulation and rule checks for DDR4 memory interface design and analysis

- Multi-gigabit serial link design and analysis featuring compliance testing for popular interfaces such as PCIe 4.0

- Streamlining the flow between IC design and package/PCB design

- PCIe 4.0 controller and PHY bring-up and interoperability

Technical & Sponsored Sessions include:

- Team-Based PCB PDN Design Methodology Enabled by IC Target Impedance Constraints

- Achieving Double Data Rates with Forward Error Correction Encoding

- Using Automated IBIS-AMI Modeling Tools to Model Advanced SerDes IP

- A Practical Simulation Solution for System-Level ESD Analysis

- LPDDR4 Signal Integrity Design Optimization Techniques for Developing Higher Quality Mobile Products

- Heterogeneous System-Level Integration Driven from the Virtuoso® Platform

- Enabling Accurate and Efficient 3D Full-Wave Extraction for Both 3D Experts and Non-Experts

- Efficient On-Chip 3D Electromagnetic Modeling Driven from the Virtuoso Environment

- Heterogeneous System-Level Integration Driven from the Virtuoso Platform

Anritsu: Booth 633

In its booth (#633) at DesignCon 2017, Anritsu will demonstrate a 56G/112 NRZ and PAM4 accurate jitter tolerance test system featuring the signal quality analyzer (SQA) MP1800A BERT with the G0374A 64 Gbaud PAM4 DAC and MP1825B 4-tap emphasis that is well suited for the high accuracy and margin requirements of communications standards such as OIF, IEEE, and InfiniBand. For high-speed serial bus verification, the MP1800A will be integrated with the MP1825B and MG3710A vector signal generator to conduct jitter tolerance tests on PCIe and 100GE interfaces.

The MP1800A will also be configured with the ShockLine™ economy vector network analyzer (VNA) MS46322A, along with Granite River Labs calibration and receiver test software to create an automated, simple, and efficient method to test Thunderbolt 3 receiver CTS. To support the latest USB3.1 Gen2 SuperSpeed+, 10 Gbit/s receiver test standards, Anritsu will show the MP1800A with its new USB3.1 receiver test adapter G0373A and dedicated high-speed serial data test software.

Also in the Anritsu booth will be the VectorStar® VNAs in multiple configurations. One station will include a 70 GHz 4-port signal integrity solution and another will be a 4-Port 70 kHz-110 GHz broadband VNA solution for on-wafer device characterization.

Anritsu will host technical and sponsored sessions, as well, including:

- De-embedding Sensitivities, Symmetry and Differential Pair Coupling.

- Signal Integrity: VNA Applications

- Toward 400G (IEEE802.3 and CEI) 56G PAM4 Bit Error Rate Test Solution.

EMSCAN: Booth 211

EMSCAN, exhibiting at DesignCon booth#211, will be demonstrating how it has significantly improved the speed and the resolution (0.06 mm) of the world’s fastest EMC/EMI scanner: the EMxpert ERX+. The company says that PCB and design engineers can diagnose EMC/EMI issues on a 2.25 cm x 2.25 cm (0.89” x 0.89”) sized PCB at 0.1 mm in less than 9 minutes. The company will also be focusing on its RFxpert RFX2 and Phantom Head+Hand kit, which enables designers to perform over the air (OTA) performance and total radiated power (TRP) measurements of mobile devices at the lab bench.

ANSYS: Booth 943

At DesignCon, ANSYS will be focusing on physics-centric simulation as it relates to advanced driver assistance systems (ADAS), IoT and 5G. ANSYS will explains how its products solve highly complex electronic assemblies and automatically produce transient plots for TDR, eye diagrams, and compliance reports. Other features include: DC analysis, map Joule heating to a mechanical solver, then produce temperature profiles and associated mechanical deformation and stress. The company will demonstrate its a chip - package - board solution that allows you to evaluate electrical, thermal, and structural behavior. Demonstrations at Workstation 1 will focus on signal-integrity, power-integrity, and EMI applications using

ANSYS Chip – Package – System (CPS) design flow In addition, this workstation will demonstrate the company’s new Chip Package Analysis (CPA) solver available within SIwave, which extracts power and signal nets on electronic packages.

Workstation 2 will focus on thermal efficiency and mechanical reliability. ANSYS will feature its new automated thermal analysis from SIwave that streamlines EM-thermal coupled analysis and links to ANSYS Mechanical for analysis of the structural impact on the electronic package.

See you at DesignCon! Signal Integrity Journal will be at tabletop T2. Use the promo code "INVITEME147" to save 15% off an All-Access or 2-Day pass, or claim a complimentary Expo Pass, at www.designcon.com/.