The role of stackup design in the development of a PCB has been around almost as long as the boards themselves have. Traditionally, the design-to-fabrication process involved the PCB developer completing the layout and schematic and then passing the design on to the fabricator who was responsible for the stackup. This process has been the “defacto standard” for designing and fabricating a board because, until now, the primary issues of concern have been impedance control and ensuring enough layers to route all the signals.

Over the years, the complexity of PCBs has changed as boards have increased in size, often with 18 or more layers. Components contain more functionality in ever-shrinking footprints; there are an increasing amount of transmission lines, which have also become thinner. Product reliability must endure a wide range of temperature and environmental conditions, and product life cycles are measured in years, if not decades. Despite these significant changes to the PCBs themselves, the ownership of the stackup, in many instances, has remained with the fabricators; this notion which has been deeply entrenched in the industry. Fabricators eventually became responsible for getting the impedance calculations correct.

Today’s high data rate/high frequency designs require a change, not just in terms of how stackups are done, but in terms of the mental approach to their design. This is especially true as the industry strives to move forward, trusting that the design to manufacturing process has been optimized and readily fits into the model-based systems engineering product development process that is becoming predominant within the industry.

The factors outlined below aim to ensure the reliability of PCB stackups from the initial design phase to manufacturing to deployment in the field, as well as throughout the long-term life cycle of the product. With today’s tight tolerances and shrinking wriggle room for operating boundaries, single points of failure can occur in any phase of the process from design to product realization. Mistakes made during the stackup process and the ensuing product failures have led to missed market windows, astronomically high non-recurring engineering costs for product redesign, and ultimately, the loss of promising companies that were not diligent enough about their PCB design processes.

A Brief Overview of a Stackup

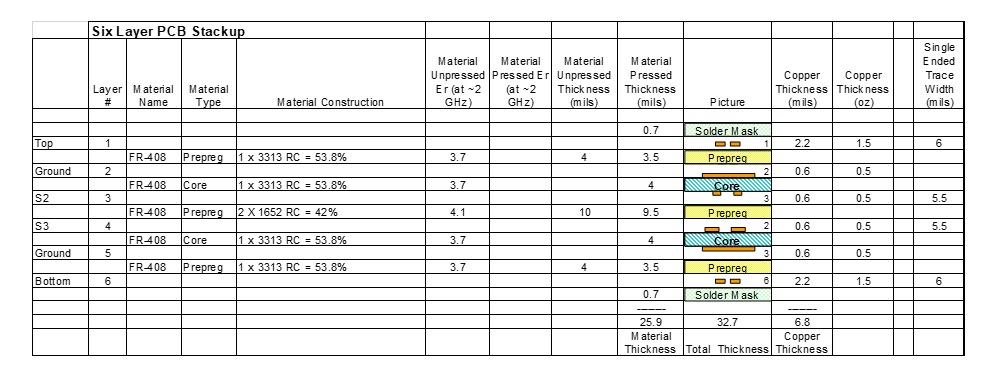

A stackup or stackup drawing shows the arrangement and types of layers in a multilayer PCB. The stackup drawing should include the exact type of laminate, prepreg, and copper that is to be used at every point in the design. The specification of these elements should not be left to the fabricator because they may not have the knowledge necessary to make the right choices. More importantly, it is not really part of their job.

A complete stackup specification for a 6-layer PCB is shown in Figure 1. It contains the information noted above (prepreg, core, and copper thickness) along with the other appurtenant elements. (For interesting information on a recent turn in the industry relative to copper foil, please read the sidebar accompanying this article).

Additional Factors

For high data rate/high frequency designs, there are additional factors to consider including:

- Dielectric Loss

- This is a property of the glass cloth and resin system that is part of the laminate. Low loss laminates are the materials of choice for high-speed designs.

- Skin Effect Loss

- High frequency currents have the tendency to concentrate near the outer edge or surface of a conductor rather than flowing uniformly over the entire cross-section of the conductor.

- The surface roughness factors into skin effect as the rougher the copper the more resistance the current faces at high frequencies.

- High frequency currents have the tendency to concentrate near the outer edge or surface of a conductor rather than flowing uniformly over the entire cross-section of the conductor.

- Skin Depth

- This is the depth that the current penetrates the copper at a given frequency.

- This effect has the tendency to occur when the frequency is higher.

- The effective resistance increases at higher frequencies where the skin depth is less. This causes a reduction in the effective cross-section of the conductor.

Figure 1. A complete PCB stackup drawing. Courtesy of Speeding Edge.

Figure 1. A complete PCB stackup drawing. Courtesy of Speeding Edge.

Today's Design Challenges

As we continue to wring the last bit of functionality out of traditional PCB technology, there is little “wriggle room” for errors, and factors beyond impedance control and signal line routing come into play, including:

- Path loss

- Skew

- Very complex power delivery engineering

- Manufacturability issues such as:

- Resin Starvation and Glass Stop

- During lamination the resin will flow out of a prepreg to fill the etched away parts of the adjacent copper layers. Ideally, there is still a butter coat that remains on either side of the glass cloth, separating the copper from it. If there is not enough resin in the prepreg, the glass fibers will come in contact with the copper. This is referred to as glass stop, which can lead to voiding, drill-induced crazing, or, worse still, conductive anodic filament or hi-pot failure. Any of these conditions can become single points of failure for a PCB under manufacture.

- Via Reliability

- Higher layer count HDI designs have led to the rapidly expanding use of microvias. With 3+N+3 and even more sequential laminations the use of skip vias, staggered and stacked microvias becomes essential. These smaller holes don’t go all the way through (as plated through holes do) and they are much more sensitive to stress and are more likely to fail during reflow, accelerated testing, or in-service conditions. The greater number of microvias that are stacked causes them to be much more likely to fail, and it is difficult to manufacture them repeatedly in high volumes. If they are successfully manufactured, the yield rates are significantly decreased.

- Resin Starvation and Glass Stop

While the foregoing is not an exhaustive treatment of all the factors that need to be addressed during the creation of a stackup that is readily documented and provided to a fabricator, it is pretty easy to see why the various material issues, structural issues, and performance factors need to be taken into account from the beginning of the design process. The PCB product developer is the best person to address them as part of the design stackup process.

Delving into this a bit further, two very similar stackups are presented in Figure 2. Figures 2a and 2b are both expected to meet signal integrity requirements, but Figure 2a is expected to fail in reflow, while Figure 2b is expected to survive with the same via structure and reflow profile. Both are complete stackups, but only the one in Figure 2b is a complete and viable stackup. The difference between the two is that in Figure 2b, the prepregs that the microvia goes through have lower expansion. This, in turn, results in lower strain on the microvia than in the case presented in Figure 2a.

Figure 2a. A stackup that is expected to fail reflow.

Figure 2a. A stackup that is expected to fail reflow.  Figure 2b. A stackup similar to that in Figure 2a that is expected to survive reflow.

Figure 2b. A stackup similar to that in Figure 2a that is expected to survive reflow. As with most aspects of today’s high data rate/high frequency designs, the answer is not a simple one. There are more factors in the stackup process, and they may well be the most difficult to address. Perhaps the simplest manner to catch and solve these kinds of problems is that the designer must take ownership of each stackup attribute and ensure its simulation.