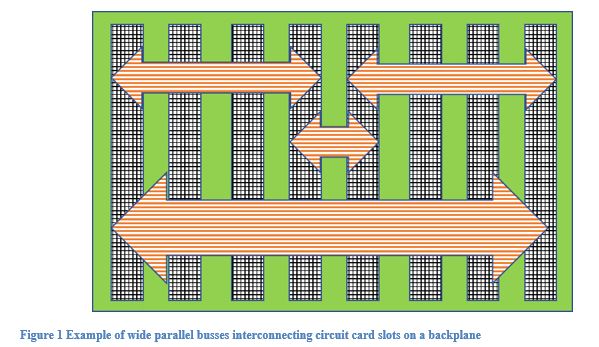

Before the high-speed serializer/deserializer (SerDes) technology we know and love today, the only way to interconnect circuit cards in a backplane was to use wide parallel busses to interconnect them as shown in Figure 1. These buses were usually limited up to 33 MHz.

Flashback to the mid 1990s: Northern Telecom (NORTEL), needed to replace the computing module shelf of the DMS Supernode switching platform because it was projected to run out of steam a few years later. In order to address the issue, the system architects concluded that a scalable, multi-processing, shared memory, computing architecture was needed to replace it. It was later to be known as Extended Architecture Core (XA-Core).

At that time, I worked at Bell Northern Research (BNR), NORTEL’s research and development labs. My task was to develop a concept to package all these cards in a shelf, and then design a backplane to interconnect everything. It quickly became apparent that a single shared backplane bus could not support the bandwidth and latency required for multi-processing. Nor could multiple parallel buses solve the problem, because of the lack of high-density backplane connector technology needed for all the I/O. Even if we had a suitable connector, and it could magically fit within the confines of the card slot, the layer count would have grown exponentially.

No, something else was needed. Fortunately, BNR had an advanced technology group that liked to play in the sand and experiment with new ideas. I remember going to a meeting one day to see some presentations on some of the neat technologies they were playing with.

One particular presentation they gave was of a unique, non-contact interconnect technology. I immediately saw the potential that technology offered to solve our problems. After a few days of sketching out some shelf packaging and high-level trace routing options, I came up with some concepts which eventually led to a patented, proprietary point to multi-point interconnect solution operating at 1GB/s per pair [1]. Unheard of in 1994!

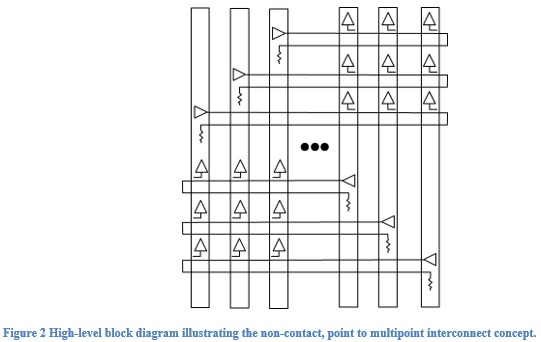

The non-contact technology actually relied on controlled electro-magnetic coupling, or simply crosstalk (see Figure 2). In this simple high-level block diagram example, each circuit card on the shelf would transmit their serial data on printed circuit board (PCB) traces across the backplane. As the differential pairs traversed through the connector pin fields, the transmit signal traces were edge-coupled to adjacent small traces called couplers, about three quarters of an inch long. They were connected to their respective receiver pins on the plug-in cards. After the last card slot, the signals switched layers and returned back to the originating plug-in card, where they were terminated.

The beauty of this architecture was that each circuit card only needed one transmitter to broadcast its data to all the other cards. Since each card had enough receivers to listen to all the other cards in the system, the point to multi-point interconnect achieved the equivalent of a point-point mesh architecture, but without the overhead of additional pins and PCB layers. Furthermore, the effective line rate of 1GB/s was achieved using simple, inexpensive 2mm HM connectors. These were the same ones chosen for compact PCI standard back in the day.

Figure 3 is a portion of an inner layer core of the backplane, prior to lamination and drilling showing the couplers in more detail. The round pads are for the connector vias, and they are used to attach the coupler traces to the connector pins. Differential receivers are connected to these pins on a plug-in card. The rows of pads on the left are for one card slot, while the rows of pads on the right are for another.

If we look at the two traces, entering the picture from the left side, they are part of a differential pair, connected to a transmitter on some other card. Each pair was routed using single-ended traces, i.e. with no coupling to one another. As these traces approach the first row of pads, they jog down to ensure close coupling to the coupler traces attached to the pads. The close coupling continues to the next set of pads, and the pattern starts all over again, as the pair exits the picture at the right. This pattern repeats all the way up the photo for each differential pair.

You may be astute to notice that the bottom coupler trace connects to a grounded pad at the far-end, while the mate coupler above it does not. Obviously, this was intentional. But why was it done; you might ask? The following explains some of the physics behind this patented technology [2][3].

When two, coplanar parallel traces are in close proximity to one another, there are two types of crosstalk generated; backward, or near-end crosstalk (NEXT); and forward, or far-end crosstalk (FEXT). Generally speaking, traces routed in stripline are only susceptible to NEXT. While in microstrip, they are susceptible to both. Since non-contact technology relies on NEXT, all routing was done in stripline.

As the transmit signal propagates, from left to right in Figure 3, the rising and falling edges of the transmit signal initiates NEXT at the beginning of the coupled length. The NEXT voltage normally saturates after a critical length equal to the risetime (tr) divided by twice the propagation delay (2tpd); where the risetime is in seconds, and propagation delay is in seconds per unit length. But since the risetime was greater than twice the time delay (2TD), it never saturates. Because of differential signalling, NEXT voltages have opposite phase on the respective couplers.

At the coupler via, there is a reflection caused by the impedance discontinuity of the via and connector pin. This reflection propagates towards the far-end of the coupler (left to right). If both couplers at the far-end are left open, any secondary reflections reflect back towards the receiver with the opposite phase. When both reflections arrive back at the receiver, they add together, and combine with the received signal. This causes inter-symbol interference, as seen by the shoulder on the trailing edges, on the eye waveform in Figure 4(A).

By leaving one coupler at the far-end open, and shorting the other one to ground, any secondary reflected noise will have the same phase. Now, when they arrive back at the receiver, they will cancel; thereby eliminating the inter-symbol interference and increasing the eye amplitude, as shown in Figure 4(B).

You will notice that the eye waveforms do not resemble the traditional non-return to zero (NRZ) eye diagram we are used to seeing. Instead we observe a typical NEXT eye, when the coupled length is short, compared to the risetime. There is also a line right in the middle.

This can be explained by referring to Figure 5. The blue waveform is the NEXT voltage, seen at the near-end of the coupler, in response to the red transmitted waveform. Notice that there are only pulses at an edge transition of the transmitted waveform. A rising edge creates a positive pulse, and a falling edge generates a negative pulse. The duration of each pulse is twice the time delay of the coupler length.

The receiver uses simple peak-detectors and latch to regenerate the signal back to the original waveform. A positive going pulse is detected by the positive peak-detector. When it crosses the positive voltage threshold (+Vth), it sets the latch output to logic high. The output remains high until a negative pulse crosses the negative threshold (-Vth), of the negative peak-detector, and resets the latch to logic low.

And there you have it. The necessity of DMS Supernode computing module capacity evolution led the way to next generation XA-Core platform. In my opinion, it was one of the last great advanced technology driven programs of its time to come out of NORTEL and ultimately lead to the invention of the POINT TO MULTIPOINT NON-CONTACT INTERCONNECT BUS [1]. A perfect example of the old saying, “necessity is the mother of invention.” It was also one of the most exciting times of my career.

References:

[1] L. Simonovich et al, U.S. Patent 6,091,739, "HIGH SPEED DATA BUS UTILIZING POINT TO MULTI-POINT INTERCONNECT NON-CONTACT COUPLER TECHNOLOGY ACHIEVING A MULTI-POINT TO MULTI-POINT INTERCONNECT."

[2] J. Williamson et al, U.S. Patent 6,016,086, "NOISE CANCELLATION MODIFICATION TO NON-CONTACT BUS."

[3] Alexandre Guterman, Robert J.Zani, "Point-to-Multipoint Gigabit Backplane Design", IEEE International Symposium on EMC, May 11-16, 2003.