Randy White

Randy White is the Memory Solutions Program Manager for Keysight Technologies. He is focused on test methodologies for emerging memory technologies in server, mobile and embedded applications. Randy has spent the last 20 years investigating signal integrity measurement techniques including de-embedding algorithms, measurement/model correlation and high speed measurements for real-time & sampling oscilloscopes as well as BERTs & AWGs. He has participated on many standards committees including PCI-SIG, USB-IF, UCIe, and JEDEC to help define new test methodologies and is currently the chair of the JEDEC JC40.5 Logic Validation subcommittee. He graduated with a BSEE from Oregon State University.

Memory Solutions Program Manager, Keysight Technologies

ARTICLES

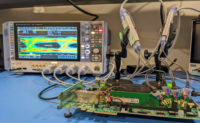

DDR5 Electrical and Timing Measurement Techniques

Read More

How to Optimize Probing and Signal Access for DDR5 System Validation

DDR5 Electrical and Timing Measurement Techniques

Read More