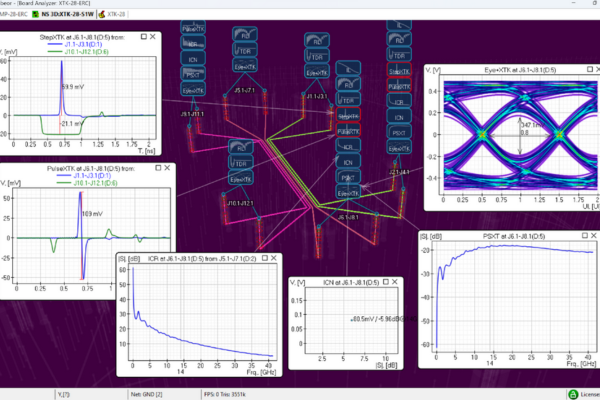

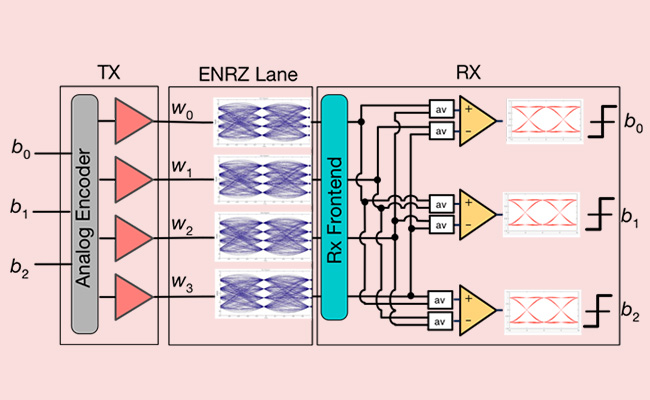

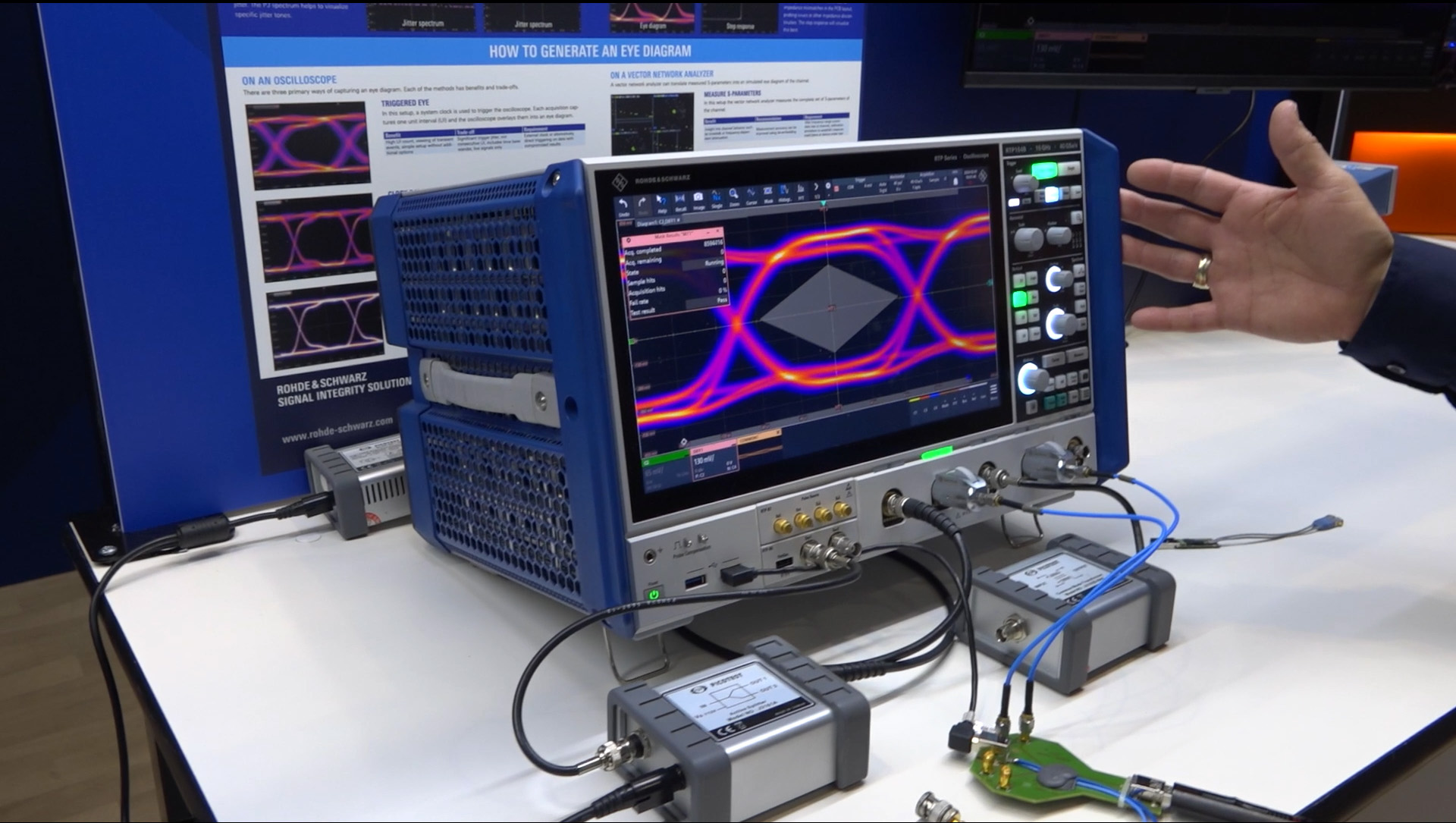

High-speed digital links at 224 Gbps per lane, device miniaturization, and ultra-low power budgets result in sophisticated systems that are more complex to optimize signal integrity performance and reliability. Engineers require close collaboration and seamless flows from concept to simulation, emulation, and testing to keep up with technology's pace and meet shrinking time-to-market expectations.

This eBook covers how to connect design workflows to make end-to-end high-speed digital design a reality. It will discuss the challenges and trade-offs associated with optimizing design performance for technologies such as PCIe 6.0, USB4 Version 2.0, and USB-C, DDR5, and LPDDR.

-Analysis-Cover-9-3-24.jpg?t=1725381744)