Many designs today include three different value decoupling capacitors, or when using just one capacitor, a small value like 0.1 uF. These recommendations are based on 50-year-old assumptions that do not apply today. It is time to reconsider these out of date, legacy design guidelines.

Myths as Legacy Code

From its inception, the electronics industry has been pulled into the future by the four forces of faster, smaller, cheaper, now. This has spurred the continual advance of revolutionary and evolutionary developments in technology, materials, manufacturing, and design. Sometimes, the design principles we adopt in an earlier generation become “legacy code” in the next generation and no longer apply. What worked for one combination of interconnect technologies may not apply to a new combination. The legacy design guideline becomes a myth and should be re-evaluated.

The Only Constant is Change

Our industry has seen revolutionary advances from tubes, to transistors, to integrated circuits, to systems in packages. We have experienced the revolutionary advances from discrete wiring, to single and dual layer printed circuit boards, to multilayer boards, to HDI technologies. We have seen the revolutionary advances from early through-hole devices such as simple metal can packages to DIPs to large pin grid arrays, into surface mount packages with lead frames to small organic printed circuit substrates to ball grid array to chip scale packages, and to multichip modules. A snapshot in time with four representative technology generations of boards and packages is shown in Figure 1.

Figure. 1 Four snapshots in time. From left to right: tubes and discrete wires, tubes and circuit boards, discrete transistors and circuit boards, and surface mount BGA packages with multilayer circuit boards.

Impact on Design from Technology Generations

The fundamental principles behind how signals interact with interconnects has not changed. They are still based on the 150-year-old Maxwell’s Equations. However, how we implement the design principles and turn them into design guidelines has evolved with each generation of packaging and interconnect technology.

In the early days of tubes using discrete wiring, often, the interconnects were transparent. When interconnects mattered, the first problem to break was usually cross talk due to large loop inductances. Design principles of “shorter is better” and power and ground wires bundled together were popular.

When multi-layer boards were introduced, some of this legacy code continued with routing power and ground as discrete wires rather than using ground planes. The legacy of keeping power and ground bundled close together held back the implementation of ground planes in some early designs.

As clock frequencies rose above 20 MHz, transmission line effects began to dominate, and controlled impedance, routing topologies, and termination strategies became important driving forces in the design of interconnects. The legacy code of “shorter is better” contributed to some reluctance of using daisy chain routing topologies which might have resulted in longer path lengths but lower reflection noise.

When we entered the 1 Gbps regime, losses became important, and we started selecting other materials besides the common epoxy-glass based ones in order to engineer lower loss. When using these lower loss laminates we found that above 5 Gbps the copper losses were higher than expected, and we found smoother copper was better. Above 10 Gbps, we found that the 50-year-old approach of building glass-fiber-reinforced circuit boards contributes to a new problem of glass or fiber weave skew.

With new technologies, we need new design rules. The old rules of high peel-strength, epoxy glass circuit boards are not necessarily the best design guidelines in the era of multi-gigabit interconnects.

Industry Experts Lead the Way

The design guidelines we apply on a daily basis in our electronic products have been developed by the industry leaders. These are the companies with dedicated experts in signal integrity, power integrity, EMC, materials, manufacturing, reliability, and integration, who are introducing products at the bleeding edge. These experts apply fundamental principles to establish design guidelines for the new materials, IC technologies, and interconnect technologies they introduce.

But sometimes, what worked in one generation of technology becomes a myth in the next generation. Because these design rules were established by experts, the rest of the industry is sometimes reluctant to let go of the older design guidelines and continues to use them in the new generation of technology where they may not apply. They become myths entrenched in our toolbox.

If the last design worked following these old design guidelines, it is often believed it was because of the design guidelines, even though it might have been in spite of them. Sometimes the legacy code is a neutral, sometimes it has a downside. Even if it is neutral, if it keeps a better design guideline from being established, it becomes a negative. It becomes a myth ready to be displaced.

A design guideline myth, like using three different capacitors per power pin for decoupling, that detracts from performance in a next-generation design should always be re-evaluated.

High-Frequency Capacitors

The ideal equivalent electrical circuit model of a real capacitor is well described by a simple series RLC circuit when the mounting inductance is larger than about 1 nH. When it is below 1 nH, new effects appear and a transmission line model for the real capacitor is a better match.

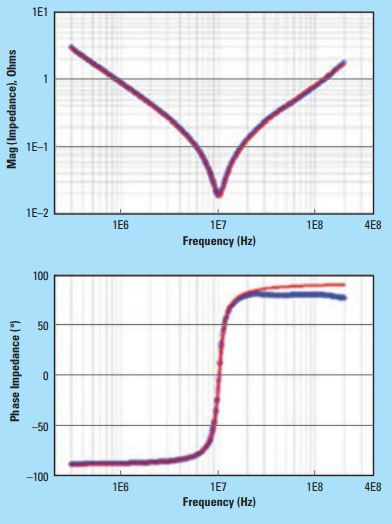

The simple RLC model applies to most generations of capacitors. An example of the measured impedance of a real SMT, MLCC capacitor and the simulated impedance of an ideal RLC series circuit is shown in Figure 2.

Figure. 2 An example of the measured impedance (in blue) and phase of a real SMT capacitor and the simulated impedance (in red) of a simple RLC circuit model. The difference in the measured and simulated phase is an indication of ESR behavior in the real capacitor not included in the simple RLC model.

This series RLC circuit model is the simplest model that generally applies across the technology range of electrolytic, tantalum, ceramic, MLCC capacitors, as either through-hole or surface mount. This is only a first-order model and many real capacitors can be matched much better with second-order models. But this first model offers insight on the role of these three important terms.

The ideal C corresponds to the impedance behavior at low frequency. The R is often referred to as the equivalent series resistance (ESR). It is due to the real capacitor’s leads, the metallization of the plates, and, to a smaller extent, the other loss mechanisms in the capacitor. The L is referred to as the equivalent series inductance (ESL). It is primarily due to the internal structure of the capacitor and its circuit board power and ground paths to the IC pins to which it connects.

In the days of through-hole capacitors, starting more than 50 years ago, two commonly used capacitor technologies were electrolytic and ceramic disk. Examples of these are shown in Figure 3.

Figure. 3 Examples of electrolytic and ceramic disc capacitors. The smaller physical size capacitors have less capacitance, smaller ESL, and larger ESR.

In both electrolytic capacitor and ceramic disc capacitor technology, there is a direct connection between the amount of capacitance that can be engineered in a capacitor and its physical size and lead length. A larger value capacitance means a larger physical size capacitor.

Because the ESL also depends on the physical size of the capacitor and its lead length, larger value capacitors also have larger ESL. For example, a 47 uF electrolytic capacitor might have as much as 30 nH of ESL, while a small 0.1 uF disc capacitor might have an ESL as low as 7 nH.

Even the ESR varies with capacitor technology and size. An electrolytic capacitor might have an ESR on the order of 0.1 to 5Ω. Smaller size capacitors generally have higher ESR. A ceramic disc capacitor can have an ESR on the order of 0.1 to 1Ω.

This connection between capacitance value and ESL dramatically affects the impedance profile of a large and a small value capacitor. At low frequency, the impedance of a real capacitor is about its capacitance. At high frequency, the impedance of a real capacitor is about its lead inductance. Figure 4 shows an example of three different capacitors with three different impedance profiles. The component values of their first order model might be:

Figure. 4 The simulated impedance profile of these three capacitors. The smallest value provides the low impedance at high-frequency.

With through-hole capacitors having leads, it generally is correct that smaller value capacitors are smaller size and can be mounted with lower loop inductance. This means they will have a lower impedance at higher frequency. When looking for a through-hole capacitor with low impedance at high frequency, choose a small value and small size capacitor.

This is why small value capacitors are often referred to as “high-frequency” capacitors. Due to their shorter leads, if mounted to the circuit board with low loop inductance, they offer the lowest impedance at high frequency.

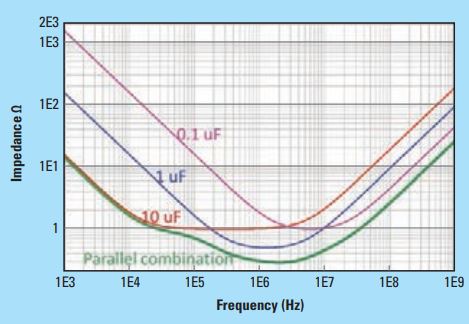

If we want the lowest impedance at low frequency as well as the lowest impedance at high frequency, a common practice has been to add two or three capacitors in parallel. A large value capacitor provides the low impedance at low frequency and a small value capacitor, with its lower ESL, provides the low impedance at high frequency. The parallel combination leverages the best of both configurations.

MLCC Capacitors and the Myth of the High-Frequency Capacitor

When we switch to capacitors based on MLCC surface mount technology, the capacitor properties are very different from leaded capacitors. Figure 5 shows examples of 1206 style MLCC capacitors with capacitance values corresponding to the same capacitance in the corresponding ceramic disc capacitors.

Figure. 5 MLCC capacitors in 1206 packages (top) and corresponding value ceramic disc capacitors.

Often, a wide range of capacitance values can be obtained in exactly the same body size. It is just as easy to have 10 uF in an 0402 as a 0.01 uF. This means that the ESL of an MLCC capacitor, if optimally integrated into a board, will be independent of its capacitance value.

In fact, using low-loop inductance designs, the ESL of an MLCC can be engineered to be less than 1 nH, even on a two-layer circuit board. An example of the measured impedance profile of a 1 uF MLCC capacitor on a two-layer 063 mil thick board with 0.620 nH ESL is shown in Figure 6.

Figure. 6 An example of the measured impedance profile of a 1 uF MLCC capacitor on a circuit board with 0.620 nH of ESL. This also shows the need for a 2nd order model when the mounting inductance is less than 1 nH. Measurement courtesy of Picotest .

A 10 and 0.1 uF MLCC capacitor will have exactly the same high frequency impedance. The smaller capacitance value capacitor is no longer a “high-frequency” capacitor. In fact, a 10 uF MLCC capacitor will also be a “high-frequency” capacitor.

If low ESL is of value in a design, MLCC capacitors should always be used. Even a 10 uF MLCC capacitor can have less than 10 percent the ESL and the impedance of a “high-frequency” ceramic disc capacitor.

In older products, when through-hole capacitors were used, smaller value capacitance had lower ESL and lower impedance at higher frequency. When there was room on the board for only one capacitor on a power pin and the transient current from that pin was small, a single “high-frequency” capacitor with low inductance was specified. This is a low-value capacitance, typically 0.1 uF.

When there was room for three capacitors for a pin, a range of three capacitor values was typically specified. This provided the lower impedance at high frequency and lower impedance at low frequency than just one value capacitor. Figure 7 is an example of a typical schematic showing these common specifications.

Figure. 7 An example of a typical circuit showing a decoupling network with three different capacitor values and a small value single capacitor.

However, this schematic example was taken not from an old design using through-hole parts and through-hole capacitors but instead from a 120 MHz leading edge Cortex M4 microcontroller board, designed and assembled all with MLCC capacitors. The myth of the high- frequency capacitor has carried over into this design as it has in many others that still specify a small value capacitor used as a single capacitor and three different values for higher current pins.

The myth of the high-frequency capacitor and the use of three different capacitor values is legacy code that is still present in many modern designs.

Which is Better?

So, which is better: three capacitors a decade apart in value or three capacitors of the same value?

Unfortunately, only a system-level analysis with accurate models of all the elements will have a chance of answering this question.

If the recommendation in the spec is to use three different value capacitors, chances are good the engineer who wrote the spec never did any analysis and is using a 50-year-old design guideline based on the myth of the high-frequency capacitor. The rationale behind this recommendation disappeared with the introduction of the MLCC capacitor 20 years ago. Be suspect of the PDN design.

In this case, it probably does not matter what you use. Your product may work in spite of the capacitor values, but probably not because of them.

When three different value capacitors with the same ESL are combined in parallel, two parallel resonance peaks are generated between their self-resonant frequencies. The peak impedance values are related to capacitance and inductance of the adjacent capacitors, and the ESR of the capacitors.

Figure 8 shows the simulated impedance profile of three different combinations of three capacitors each. One combination is the recommendation for 10, 1, and 0.1 uF implemented in through-hole technology. The second is the same combination implemented in MLCC capacitor technology. The third combination is all the same 10 uF MLCC capacitors. The ESL of the MLCC capacitors is 1 nH.

Figure. 8 The simulated impedance profiles of three different and three identical MLCC capacitors.

Three capacitor values all the same large value may provide lower impedance across the spectrum than three different value capacitors (and without the parallel resonant peaks at intermediate frequencies), but this does not mean it is a more robust solution.

The last product might have worked, but you may have no idea how robust the design is or whether some of the untraceable, non-reproducible failures might have been due to excessive switching noise with just the right convergence of data patterns that saw a marginally high impedance at a parallel resonance.

Do not be lulled into thinking that three different values of capacitors is a robust strategy, or that three capacitors all the same value is more robust. Without a system level analysis, they both may be equally acceptable, equally marginal, or fail from the same faults.

“Test-In” Quality

If you are not going to do your own system level analysis, plan to implement a thorough test plan so that you can find the weak links in your PDN and “test-in the quality.”

Part of a thorough test plan is to design for test in the PDN. The better you can characterize noise (not just at the board level but on the pads of the die) using high bandwidth sense lines, for example, the better you will be able to compare one decoupling strategy to another. Figure 9 is an example of the measured voltage noise on the die power rail and on the board level while I/Os switch. The on-die voltage noise is 600 mV peak-to-peak on a 5 V rail. The board-level voltage noise is only 75 mV peak-to-peak.

Figure. 9 Measured voltage noise on the same power rail on the die measured through a sense line, and on the board, both scales the same 200 mV/div.

Regardless of the application, lower mounting loop inductance is always of value. This is why the MLCC decoupling capacitors should always be the second components placed on the board, so they can be routed with the lowest mounting inductance practical.

If only one capacitor is specified on a pin, as is common practice for many low-current applications, then always use the highest capacitance allowed for the smallest body size practical, at the acceptable voltage rating. Without a system-level analysis, this is still no guarantee of a robust product, and a thorough test plan is essential.

Design-In Quality: The Right Decoupling Capacitor Strategy

The use of three different values of decoupling capacitors is based on the outdated assumption that small value capacitors are “high-frequency” capacitors. In our era of MLCC capacitors, where this assumption does not apply, what is a better recommendation? Unfortunately, the answer is, “it depends.”

However, there are some general design guidelines that will apply to most systems.

The goal in any PDN is to provide a DC voltage to those components that need it, with an acceptable level of noise for the application. MLCC capacitors used for decoupling are only a part of a good PDN strategy.

One of the underlying principles in the design of a PDN is to keep the impedance profile, as seen by the pads of the IC, a flat impedance and at a value that is acceptably low. This means reduce the parallel resonance peaks generally by adding more capacitance, reduce the loop inductances, and sculpt the impedance profile either by using different capacitor values or through controlled ESR (which will reduce the q-factor of peaks).

This sometimes translates to enough bulk capacitance so that the VRM-bulk capacitor peak is reduced. At the high-frequency end, a flat impedance profile at the board level will help dampen the Bandini Mountain of the on-die capacitance and package lead inductance parallel resonance peak.

Selecting capacitor values requires a system level analysis including the VRM at one end and the consuming elements at the other. While you engineer all the mounting features to reduce the loop inductance of the capacitors as much as practical, it is always valuable to use 3D simulators and measurement-based modeling tools to develop accurate models for the PDN elements to simulate the entire system. An accurate model of the VRM and the on-die capacitance of each rail and package lead inductances are part of the overall analysis to engineer a robust design.

When there is considerable on-package decoupling, the low frequency properties of the bulk capacitors and MLCC capacitors are more important. When the on-die capacitance and package lead inductance dominate, creating a large Bandini Mountain from their parallel resonance, damping from a flat impedance profile created by the board level MLCC capacitors is important.

Unfortunately, no combination of just three capacitor values other than using controlled ESR capacitors will provide any damping at the board level for the Bandini Mountain.

This is only a glimpse into some of the design driving forces that really go into the optimized, cost-effective decoupling strategy. The first step is to identify the problem. The second step is to identify the root cause of the problem, and the third step is to determine the overall PDN design strategy which provides acceptable noise, of which the optimized decoupling strategy is only part.

When there are more than six orders of magnitude difference in the target impedance of systems, ranging from more than 10Ω in many IoT applications, to less than 10 uOhms in large network processor-based products, there is not one cost-effective strategy, but many.

But that is a story for a different chapter.

Summary

The origin of the use of three different capacitor values is based on the use of through-hole, leaded capacitors. Smaller capacitance value capacitors generally will have lower ESL and lower impedance at high-frequency. With through hole capacitors, using three different capacitor values has a performance advantage.

But with MLCC capacitors, in use for more than 20 years, these old, legacy design guidelines no longer apply.

When just one or three capacitors are specified for decoupling, it is probably because no analysis of the design was done. Instead, what worked in the last design is what is recommended in the next design. The design works, in spite of using three different values, and chances are, would work equally as well using all three the same value. In this case, the robustness of your design is “tested in” instead of “designed in.”

The best approach is to always do your own analysis, including the rest of the power distribution system and, when available, accurate models of all your components, as they are mounting into your system.

If your design specifies three different capacitor values, you may be following a legacy design guideline that has been carried forward for more than 20 years. It is probably time to reconsider this design guideline for your next design and do your own analysis.n

Further Reading

E. Bogatin, “Signal and Power Integrity, Simplified,” Prentice Hall, 2018.

I. Novak, “Comparison of Power Distribution Network Design Methods: Bypass Capacitor Selection Based on Time Domain and Frequency Domain Performances,” DesignCon, 2006.

S. M. Sandler, “Power Integrity,” McGraw Hill, 2014.

L. Smith and E. Bogatin, “Principles of Power Integrity and PDN Design,” Prentice Hall, 2018.

Article was published in the SIJ January 2020 Print Issue, Technical Cover Feature: Page 10.