What are the optimal methods (and their resulting challenges) to achieve 224/212 Gb/s common electrical I/O (CEI) and Ethernet, the highest speed/data rate per lane electrical input/output (I/Os) and link systems? By way of understanding, we begin by investigating optimal pulse amplitude modulation (PAML) vs. channel characteristics at 224 Gb/s. Then, we conduct systematical simulations and modeling with TX and RX silicon (Si) assumptions from our latest test chips in <= 10 nm process nodes, and package assumptions from the technology available in 2024-2025 when 224 Gb/s systems on chip (SoCs), optical modules, and passive copper cable will be deployed, along with three channels having BGA-to-BGA ILs in the range ~25 dB to 40 dB at 56 GHz, and sweep modulations from PAM4, to PAM6 and PAM8.

We discuss forward error correction (FEC) vs. modulation as FEC is required for all the higher order PAML where L > 4, to achieve bit error ratio (BER) < 1e-12 or 1e-15 link performance requirement. We investigate symbol error ratio (SER) and burst error propagation probability vs. with L relationship and its implication to the FEC for higher PAML where L > 4.

We then highlight Intel’s 224 Gb/s test chip measurement results (first disclosed at the Intel Architecture Day in August 2020, and the world’s first 224 Gb/s-LR-PAM4 capable transceiver demonstrated in real Si),1,2 achieving 2x improvement in bandwidth (BW), jitter, and noise, and discuss its implications and benefits to the development of a 224 Gb/s specification such as Optical Internetworking Forum (OIF)/CEI and Ethernet and ecosystems.

224 Gb/s Modulation and Channel Characteristics

Modulation schemes determine how the binary data payload is encoded/decoded before transmitting on the channel medium, and they also determine the component/link BW requirements. Currently, PAM4, which encodes 2 bits into one symbol and reduces channel BW needs by half compared to non-return to zero (NRZ). 50 Gb/s and 100 Gb/s per lane Ethernet, as well as OIF-CEI-56 G/112 G per lane electrical I/Os and links use PAM4. Naturally, it is highly desired to continue using PAM4 at 224 Gb/s, considering backward compatibility, electrical to optical compatibility, established and proven testing methodology, and equipment maturity/availability.

From the transceiver point view, to continue using PAM4 modulation at 224 Gb/s, the symbol rate, BW for the analog front-end (AFE) needs to increase by 2x, yet jitter and noise spectrum density need to be reduced by 2x to the first order, compared with 112 Gb/s PAM43 has demonstrated that performance doubling can be achieved with Intel 10 nm FinFET process technology. It is anticipated that the performance will be further improved with advanced and smaller node beyond Intel 10 nm.

To support 224 Gb/s PAM4, end-to-end channel (including package, break-out, PCB/cable, and connectors) performance needs to improve such that the insertion loss (IL) at its Nyquist will be at the vicinity of those for 112 Gb/s. Good progress has been made in the industry in achieving those goals.

We conducted a set of experiments to study the relationships among the modulation schemes, channel characteristics, and transmitter/receiver characteristics via time-domain end-to-end link simulations.

Simulation Configuration:

-

Data Rate: 224 Gb/s

-

Modulation Scheme: PAM4, PAM6, PAM8

-

Test Pattern: PRBS-31 with PAM4/PAM6/PAM8 coding Transmitter Configuration:

-

20 to 80 percent Rise/Fall Time: Correlated to Intel 224 Gb/s test chip1

-

AFE Characteristics: Correlated to Intel 224 Gbps test chip1

-

TX EQ: 4 pre-taps and 1 post-tap

-

Separation Level Mismatch (RLM): 0.95

-

Jitter: duty-cycle distortion (DCD): 0.019 UIpeak-peak, bounded uncorrelated jitter (BUJ): 0.04 UIpeak-peak, random jitter (RJ): 0.01 UIRMS

-

Noise: 11.19 mVRMS (corresponding to transmitter output SNR of 33 dB)

-

Package: 31 mm, per Intel package 2024-2025 projection

Receiver Configuration: -

AFE Characteristics: Correlated to Intel 224 Gbps test chip1

-

RX EQ: continuous time linear equalization and RX FFE+DFE: three pre-tap, 24 post-tap, floating taps with six banks of three consecutive taps up to 80 taps

-

RX Jitter/Noise: RX input referred noise: 4.1x10-9 V2/ GHz

-

Package: 29 mm, per Intel package 2024-2025 projection

-

The channel characteristics of all test channels is shown in Figure 1

Taking Channel #4 as an example, it is characterized with ~25.3 dB IL at 56 GHz, ~21.5 dB at 44.8 GHz, and 18.5 dB at 37.3 GHz for 224 Gbps PAM4/6/8 modulation schemes and is categorized as a long reach channel. The IL deviation (ILD) characteristic is ~0.7 dB in the operating frequency range. The crosstalk (both near- and far-end) is about -40 dB. Simulation results with three modulation schemes with Channel #4 are shown in Figure 2.

The simulation results indicate that, at 224 Gb/s, the PAM4 modulation scheme outperformed both PAM6 and PAM8 schemes with ~30 dB (BGA-to-BGA) system/application. This implies that 224 Gb/s long reach links can be realized using the PAM4 modulation scheme with reasonable channel design and characteristics.

The simulation results indicate that, at 224 Gb/s, the PAM4 modulation scheme outperformed both PAM6 and PAM8 schemes with ~30 dB (BGA-to-BGA) system/application. This implies that 224 Gb/s long reach links can be realized using the PAM4 modulation scheme with reasonable channel design and characteristics.

Table 1 summarizes our 224 Gb/s PAML modulation scheme simulation experiments. It is clear that the optimal modulation critically depends on the channel performance and characteristics. Simulations have shown that with reasonable channel IL (i.e.,~ 30 dB IL and ≤ 3 dB ILD, at the PAM4 Nyquist), and a transceiver design (die and package) that works well at PAM4 rate, PAM4 would out-perform PAML, where L > 4.

224 Gb/s Modulation and FEC

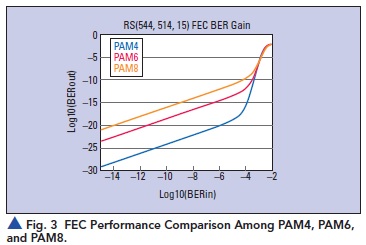

FEC becomes mandatory for PAM4 modulation starting from 50G Ethernet and 56 G OIF/CEI. For a given FEC, its performance or gain degrades when the order of PAML increases. It may be tempting to say that stronger FEC than Reed Solomon (RS)(544, 514, 15), the so called “KP FEC,” would be needed for PAM6 and PAM8. It, however, would be very challenging to make it happen in standards such as 802.3 Ethernet because of their legacy and strong incentive to keep backward compatibility and/or to minimize the changes for no obvious return.

The number of the modulation symbols per FEC symbol depends on the order of the PAML modulation as summarized in Table 2. This information is used to translate the modulation symbol error to the FEC symbol error. For example, while 5 UI long modulation symbol burst may cause only one FEC symbol error with PAM4, it causes two FEC symbol errors with PAM6 and PAM8.

There are two types of modulation symbol errors: random error and burst error. Random error is caused by random noise, which may be true random noise or quasi-random noise approximating inter-symbol interference and some other noise combined together. Each PAML level has a distribution due to noise, and elementary one-side symbol error is considered. The number of such error elements is a function of the order of PAML modulation. The higher the order of the modulation level L for a given elementary one-side symbol error probability which is usually observed in an eye diagram, the higher the modulation SER. Note that higher signal-to-noise ratio (SNR) is required for higher order modulation in order to achieve the same raw SER. Requiring higher SNR means requiring larger device power. If the device power is the same, higher order modulation would result in higher SER since noise power is generally not very sensitive to device power.

The critical parameter for burst error modeling is error propagation probability. Distributed feedback error (DFE) propagation is often considered as the primary burst error source. The higher the order of the modulation for a given DFE tap coefficient use, the more chance to have longer burst error.

A FEC performance model can be created by combining the random error model and burst error model. Figure 3 shows the comparisons of KP FEC performance among PAM4, PAM6, and PAM8 with certain error propagation conditions. This example data indicates that stronger FEC would be needed for PAM6 and PAM8 while KP FEC still works for PAM4. For instance, if the maximum pre-FEC BER is 10-4, while PAM4 can achieve BER < 10-15 with KP FEC, the PAM6 and PAM8 fall short of the 10-15 BER target by quite some margin. One consequence of using stronger FEC, however, is the undesired effects of extending latency and increasing power consumptions. Therefore, it is not desirable to jump to stronger FEC than KP FEC unless necessary.

224 Gb/s Transceiver Development and Characteristics

To support 224 Gb/s PAM4, transceiver circuit performance needs to scale with Nyquist frequency from 112 Gbps PAM4. Specifically, as compared with a 112 Gb/ PAM4 transceiver, AFE BW needs to increase by 2x, TX, RX jitter (DJ and RJ) needs to be reduced by 2x, and TX and RX broadband noise needs to be reduced by 2x. Intel’s 224 Gb/s-LR-PAM4 capable transceiver achieved those objectives with an ADC/DAC full-DSP architecture.2,3 The latest full test chip measurement results are shown in Figure 4, demonstrating a CEI-224 G-LR-PAM4 capable full transceiver with clean PAM4 eye-diagrams at 212 and 224 Gb/s, and a TX-> Channel (>31 dB)-> RX LR link with a raw BER < 1e-6, exceeding the anticipated raw BER specification (i.e., 1e-4) by more than two orders of magnitude.4

Summary and Conclusion

We started with the investigations of optimal PAML modulation vs. channel characteristics at 224 Gb/s. We conducted systematical simulations and modeling with TX and RX Si assumptions from the recent 224 G-LR-PAM4 test chip, and package assumptions from the technology available in 2024-2025 when 224 Gbps SoCs and optical modules. We found that as long as channel IL is ~ 30 dB or lower at 224 Gb/s PAM4 Nyquist, PAM4 outperforms PAM6 and PAM8.

We continued the discussion with FEC vs. modulation, as it is required for all the higher order PAML when L ≥ 4. We demonstrated that SER and burst error propagation probability increases with L, which implies that more complex FEC than the currently widely deployed RS(544, 514) or KP FEC would be needed for L > 4, resulting in higher power/area/latency.

By way of example, we showed that Intel’s recent 2021 224 G-LR-PAM4 test chip measurement results achieved 2x improvement in BW, jitter, and noise. These test results provide critical and necessary information that can assist in the development of a 224 Gb/s specification for the industry and ecosystem.

Overall, our investigations presented in this paper, along with the considerations of backward, optical modulation, FEC compatibility, and broad market potential, suggest that PAM4 remains to be the optimal/common modulation for various reaches (from XSR, to VSR, MR, and LR) for 224 Gb/s electrical I/Os.

References

1. Intel Architecture Day (IAD), August, 2020.

2. Intel Next Generation FPGAs 224 Gbps-PAM4-LR Transceiver Overview.

3. J. Kim, S. Kundu, A. Balankutty, M. Beach, B. C. Kim, S. Kim, Y. Liu, S. K. Murthy, P.

Wali, K. Yu, H. S. Kim, C-C. Liu, D. Shin, A. Cohen, Y. Fan, and F. O’Mahony, “A

224Gb/s DAC-Based PAM-4 Transmitter with 8-Tap FFE in 10nm CMOS,” ISSCC 2021,

San Francisco, Calif.

4. I. Levin and K. Zhang “Intel® Next Generation FPGAs 224 Gbps-PAM4-LR Transceiver

Overview,” IFTD (Intel FPGA Technology Day), December 2021.

Additional Resources

-

Optical Internetworking Forum (OIF) Common Electrical I/O (CEI) - Electrical and Jitter Interoperability agreements for 112G+ bps, IA # OIF-CEI-05.0 (Draft), 2021

-

IEEE 802.3ck Draft 2.0, March 10, 2021.

-

IEEE Standards for Ethernet: IEEE Std 802.3TM-2018.

-

C. Liu, “What is FEC and How Do I Use It,” Signal Integrity Journal, Vol. 1, No. 2, July 2019.

Published in the SIJ 2022 Print Issue, Cover Feature: Page 8.