Anyone in attendance at DesignCon 2023 knows that 224 Gb/s PAM4 signaling is in full development, but there is still some time yet before it is actively deployed. One of the critical elements to enable these higher data transmission speeds is the transmission line performance. Traditionally, transmission lines are traces on a multi-layer printed circuit board (PCB). Recently, in preparation for 224 Gb/s and beyond, our group engaged in a research project to characterize the transmission performance of emerging PCB material sets.

Keeping in mind that systems are not shrinking in size, it would be beneficial to keep that same loss per inch as 112 Gb/s just scaled to double the frequency. However, our initial results revealed that there is some distance to go in PCB development to reach the 1.1dB/inch insertion loss expectations that some standards bodies are considering. PCB manufacturers do continually advance the state of the art to improve their material’s characteristics, most notably roughness from foil and oxide treatment Simultaneously, twinax cable technologies also continue to improve and offer an alternative to PCB transmission lines.

Our work’s aim was to explore the current state of the art for PCBs and cables, compare them, and assess the technology gap to fully support the insertion loss performance required for higher data rates. This article explains our methods and results, and points to future work in this area.

Background

The PCB and semiconductor package are responsible for the majority of loss in an electrical system, and their performance is a critical consideration for 224 Gb/s/PAM4 signaling. Our research focused on emerging PCB materials, so we asked our providers for their best foil, dielectric, and oxide treatment combination that would be next generation, mass-produced after 2024 (in some cases, the dielectric had been in production, but not with this foil smoothness). This study focuses solely on electrical performance of laminate and foil combinations, so it does not consider vital mechanical considerations, such as adhesion during processing.

This project began in 2020, and it has evolved as new laminate systems became available. While a loss per inch metric is important for evaluating a transmission medium, often the details on material and geometry choices, test fixture design, and measurement considerations are missing. This article lays bare these details (as much as can be divulged) and our care in measuring to 110 GHz for digital applications. It will also discuss the impact of conductor width (or cross-section width) on performance in addition to suggesting how temperature might impact performance.

One of the big takeaways from the project is the significance of conductor width and its impact, specifically in terms of the cross-sectional area and the associated AC resistance. Packaging devices and traditional PCB stack-ups have system constraints on the width of the conductor due to dielectric thickness, layer count, characteristic impedance targets, and density considerations, so this needs to be a careful tradeoff. Of course, removing these constraints has found recent extreme performance at 224 Gb/s exploration with proposed strategies such as “skip layer” routing.1 Alternatively, a Flyover solution quickly gets the signal off the PCB and provides significantly more cross-sectional area of copper, smooth signal conductors, as well as very low dielectric constant and loss tangent.

Measurement Setup

Figure 1 includes an image of the measurement setup where the board uses the full available panel, designed for 90 GHz, and uses 1.0mm W vertical launch RF connectors. The measurement board includes short, long, differential, and single-ended traces which were intentionally set on different angles to check fiber weave effect and maximize measurement possibilities. As we switched out the laminates in the build-up, we tried to keep the cross-sectional geometry as similar as possible. We did not re-optimize the breakout area under the SMA for each material as the dielectric constant was unverified, so we did see some slightly different bandwidth degradation in the measurements.

Figure 1. Measurement setup for 110 GHz providing two lengths for each of nine routing angles.

Figure 1. Measurement setup for 110 GHz providing two lengths for each of nine routing angles.

The 1.0 mm RF connectors are compressed on the board which has a via in pad plated over (VIPPO) laser drilled via down to layer 2, and then a transmission line over and back up, so all transmission occurs on layer 2. We chose a micro via because it has better control and is without a stub from the layer transition when compared to a traditional plated-through-hole via. These choices help to provide the highest de-embedding bandwidth.

The test fixture (see Figure 2) includes a stiffener behind the large PCB panel. It aims to hold the board perpendicular to the Keysight test head with a short 6-inch cable to strain relief the RF connectors. Testing with 1.0 mm and up to 110 GHz is challenging due to limited test flexibility of the cable reach as well as connection delicacy.

Figure 2. Test fixture that was used to extract electrical characteristics for the traces on emerging dielectric and foil combinations.Table 1 outlines the characteristics of the materials tested. In some cases, materials had to come from different factories to achieve the desired oxide etch (such as material C), which was not optimal. For comparison’s sake, Material A with a core layer thickness of 100 um was being used by our manufacturing teams at the time of the experiments. Finding emerging materials with a thickness of 100 um proved difficult. As a result, the trace width had to change in order to keep characteristic impedance targeted to at 50 Ω or 100 Ω (more on this in later sections).

Figure 2. Test fixture that was used to extract electrical characteristics for the traces on emerging dielectric and foil combinations.Table 1 outlines the characteristics of the materials tested. In some cases, materials had to come from different factories to achieve the desired oxide etch (such as material C), which was not optimal. For comparison’s sake, Material A with a core layer thickness of 100 um was being used by our manufacturing teams at the time of the experiments. Finding emerging materials with a thickness of 100 um proved difficult. As a result, the trace width had to change in order to keep characteristic impedance targeted to at 50 Ω or 100 Ω (more on this in later sections).

Table 1. Matrix of materials tracked includes five materials from five suppliers and three fabricators. (Key:

Table 1. Matrix of materials tracked includes five materials from five suppliers and three fabricators. (Key:Figure 3 shows the measurements of the materials in Table 1. For the insertion loss measurement, Figure 3 plots the longest trace for a general comparison. You can see the baseline in red versus the progressive loss performance increase as explorations in foils, materials, and conductor width were investigated on different material sets. These non de-embedded results show the general trend as well as highlight the degradation from the compression connector and the break out region (BOR) via. It is a nice contrast to the de-embedded results shown later in this paper (see Figure 7).

One unfortunate but unsurprising side note is that, as loss performance improves, the reflections start to dominate (as shown in the E5Z material in Figure 3 having increased insertion loss ripples), demonstrating the challenge of managing the reflections on the panel level as insertion loss is addressed. This is an important challenge that extends to the development of high bandwidth channels in general.

Next, we plot the phase delay for all the measurements, which gives a sense of their dielectric constant. In the two right panels of Figure 3 (phase delay), the gold-colored line (material B2X) had the fastest propagation delay, as this is a PTFE-based material. The rest of the materials are polyphenylene oxide (PPO)-based composites with a glass cloth in them which are traditionally more desirable for multilayer buildups.

Confirming Trace Geometry

Figure 4 and Figure 5 show the trace width that was targeted by the vendor (Target Singled Ended Width or Target Differential Width) as compared to the width we measured optically. For these measurements, we measured in two places on the traces and averaged the width.

Figure 5. Trace width specified vs. measured for differential signals; cross section sample.Confirming the manufactured geometry is important because the physical geometry (e.g. trace cross-section) has a significant impact on the AC resistance, characteristic impedance, and insertion loss. We found that, for the most part, the target versus measured widths were similar across all the samples. However, for E5Z the trace was not only wider than the target, but the foil was also thicker by about 30% than 0.5 oz copper as well. This suggests that the vendor used a heavier foil than the specified. Another interesting find was that the vendor substituted the core material of EZ5 with a single ply of 2116 glass weave instead of the specified two plys of 1035 glass weave. Confirming what the vendor delivered versus targeted was vital for simulation to measurement calibration.

Figure 5. Trace width specified vs. measured for differential signals; cross section sample.Confirming the manufactured geometry is important because the physical geometry (e.g. trace cross-section) has a significant impact on the AC resistance, characteristic impedance, and insertion loss. We found that, for the most part, the target versus measured widths were similar across all the samples. However, for E5Z the trace was not only wider than the target, but the foil was also thicker by about 30% than 0.5 oz copper as well. This suggests that the vendor used a heavier foil than the specified. Another interesting find was that the vendor substituted the core material of EZ5 with a single ply of 2116 glass weave instead of the specified two plys of 1035 glass weave. Confirming what the vendor delivered versus targeted was vital for simulation to measurement calibration.

Examining Surface Roughness

While the dielectric characteristics are important for insertion loss performance, it is perhaps becoming more critical, with such extreme low loss dielectrics, to understand the foil roughness that results from the laminate supplier’s choice of foil supplier as well as the PCB fabricator’s preparation and laminate processing (e.g. oxide treatment step).

Figure 6. The baseline foil roughness compared to the best foil roughness in the study.

Figure 6. The baseline foil roughness compared to the best foil roughness in the study.Figure 6 shows SEM images taken in-house at Samtec of two materials from Table 1, A1X and E5Z. Note in the top right image the foil roughness delivered by the vendor (you can see the nodules hanging off the bottom of the trace ), and the top side of the trace where the oxide treatment occurs (highlighted in blue). A1X was used as the baseline material for comparison with the others.

The bottom of Figure 6 shows the SEM images of the best performing material in the study. You can see in the zoomed in section that a lot of care was taken to achieve a low roughness foil. Again, we must stress that mechanical adhesion was not the focus of our study, and the characterization boards did not go through reflow.

Determining Loss/Inch

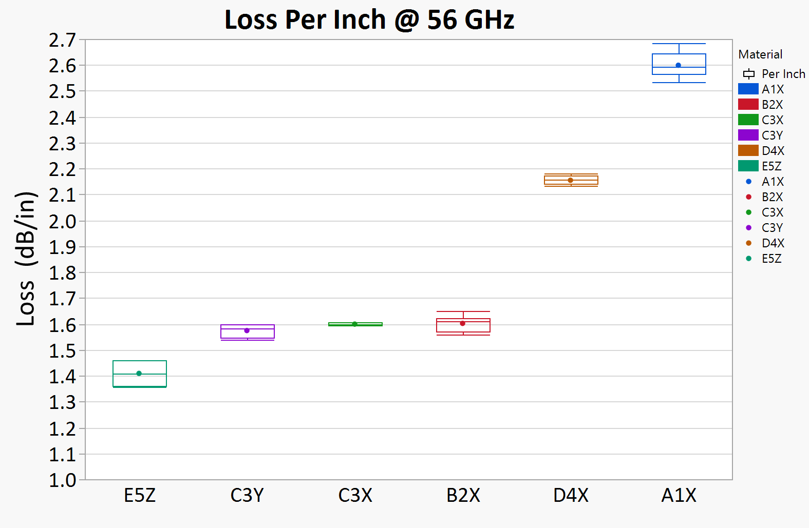

We used a proprietary de-embedding method to remove the test point with an impedance corrected 2x through algorithm in post-processing. Despite claims and roadmaps to 1.1 dB/inch loss at 56 GHz, the mean of the lowest insertion loss performance measured across several panels was 1.4 dB/inch at room temperature (see Figure 7).

Figure 7. Loss per inch at 56 GHz for each of the material sets measured. The EZ5 material measured at 54% of the baseline material, A1X.

Figure 7. Loss per inch at 56 GHz for each of the material sets measured. The EZ5 material measured at 54% of the baseline material, A1X.This analysis suggests that achieving 1.0 dB/inch at 56 GHz or lower loss performance remains optimistic at the trace width (e.g. 5 mil or below) often needed to accommodate the density of large package devices.2

Moving Forward With a Model

After the measurements and analysis were completed, the goal was to create a synthetic (frequency dependent RLGC) transmission line model to accelerate analysis of new configurations, such as trace width, without having to build new test boards.

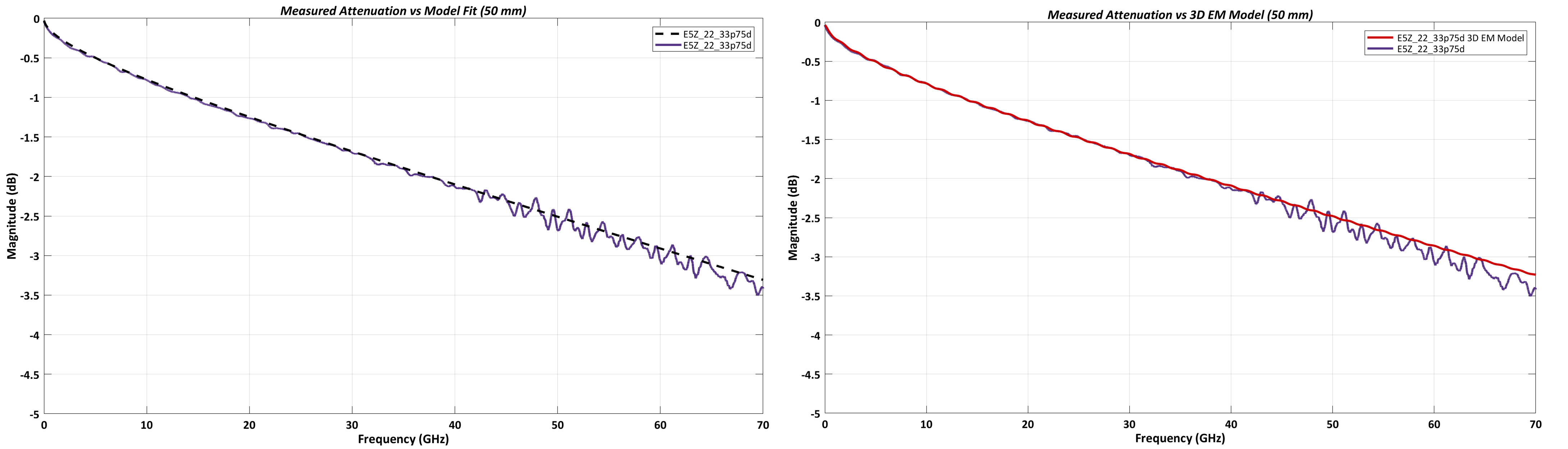

Figure 8. Fitted transmission line model fits very well out to 70 GHz for attenuation and phase delay.

Figure 8. Fitted transmission line model fits very well out to 70 GHz for attenuation and phase delay.

Figure 8 shows Samtec’s synthetic modeling that was able to fit well up to 70 GHz, and extremely well up to 45 GHz. Next, as shown in Figure 9, we used the extracted material characteristic values to create a 3D EM model to validate the results of the synthetic model.3,4,5,6

Figure 9. Comparing the synthetic transmission line model to a 3D EM model shows a good match, validating the synthetic model in Figure 8.

Figure 9. Comparing the synthetic transmission line model to a 3D EM model shows a good match, validating the synthetic model in Figure 8.

Trace Width Considerations

It is important to clarify conductor width choices for this type of analysis because many technical discussions and marketing materials talk about loss at or below 1.1 dB/in at 56 GHz, but they do not mention the conductor width. If the width is too wide for the system design constraints, it is not practical to route signals properly due to considerations mentioned above. It is also important to comprehend the impacts of temperature and humidity. In real system implementations, it is not unrealistic to expect PCB material to operate as high as 70°C due to thermal management limitations and heat transfer through the printed circuit boards.

Increasing trace width decreases loss/AC resistance, but the wider-track widths remove the opportunity for trace density. Wider trace widths also increase crosstalk if the dielectric layers are increased to achieve the same characteristic impedance. It may be possible to use lower trace impedance (such as 92 Ω or 85 Ω) to alleviate some of these consequences.

If decreasing conductor width adds loss, what is the sweet spot for trace width? We used our synthetic transmission line model to analyze the tradeoff between width and insertion loss on loss/in (see Figure 10). For comparison’s sake, we also added the insertion loss for a Samtec Flyover twinax interconnect, which is an alternative to a PCB trace.

Figure 10. Predicting trace width vs. loss using the synthetic model. Flyover Twinax curve added for comparison.

Finally, we also wanted to predict the impact of temperature on loss. The initial modeling had been at 20°C, but temperatures up to 70°C could be realistic. In a quick analysis, we assumed that the only thing changing is that conductivity of the copper foil is derated for a higher temperatures. Figure 11 plots the data that resulted from taking the coefficient for copper and applying it to the modeling, which shows more loss as temperature increases. (This does not account for any temperature or humidity effects on the polymer itself.)

Figure 11. Predicting temperature impact to loss using a 5mil width model. Assuming resistivity increases 0.393%/oC, conductivity 20oC = 5.7e7 (S/m); conductivity 50oC = 5.1e7 (S/m); conductivity 70oC = 4.76e7 (S/m). Temperature and humidity effects on the resin are not considered.

Figure 11. Predicting temperature impact to loss using a 5mil width model. Assuming resistivity increases 0.393%/oC, conductivity 20oC = 5.7e7 (S/m); conductivity 50oC = 5.1e7 (S/m); conductivity 70oC = 4.76e7 (S/m). Temperature and humidity effects on the resin are not considered.

Conclusions

Work continues in PCB development, and innovations will be required to reach the 1.1 dB/inch insertion loss specification that some standards bodies are considering.7,8,9 The greatest challenges will likely require the assistance of developments in materials science if next-generation 224 Gb/s designs continue to use traditional transmission line technologies.

References

- IPC-TM-650, Test Methods Manual, "Stripline Test for Permittivity and Loss Tangent (Dielectric Constant and Dissipation Factor) at X-Band", 2.5.5.5, Rev C, 1998.

- H. Shi, Investigation of Package Crosstalk and Impact to 28Gbps Transceiver Jitter Margin, DesignCon 2016.

- B. Simonovich, “Practical Method for Modeling Conductor Surface Roughness Using Close Packing of Equal Spheres”, DesignCon 2015 Proceedings, 2015.

- P. G. Huray, "The Foundations of Signal Integrity", John Wiley & Sons, Inc., 2009.

- A. R. Djordjevic, R. M. Biljic, V. D. Likar-Smiljanic, and T. K. Sarkar, "Wideband Frequency-Domain Characterization of FR-4 and Time-Domain

Causality," IEEE Trans. Electromagnetic Compatibility, Vol. 43, No.4, November 2001. - Y. Shlepnev, et. al, “Practical Identification of Dispersive Dielectric Models with Generalized Modal S-parameters for Analysis of Interconnects in 6 – 100 Gb/s Applications”, DesignCon 2010 Proceedings, 2010.

- B. Gore, “Measurement Evaluation of PCB Electrical Performance 200 Gb/s PAM 4,” IEEE October 2022 Series of Electronic Meetings, IEEE P802.3df.

- B. Gore, “Measurement Based PCB Performance for 224G PAM4,” Optical Internetworking Forum Q4 2022 Technical Committee Meeting, oif2022.463.02 November 2, 2022.

- N. Tracy, “Characteristics of a Passive Direct Attach Copper Cable (DAC) Assembly in CR Channels with Various Host Architectures,” IEEE July 2022 Plenary, IEEE P802.3df.Plenary, IEEE P802.3df.